Günümüzde neredeyse her elektronik cihazda bulunan işletim sistemi, yüklü olan donanımların denetiminden ve yönetiminden sorumlu olan yazılımdır. İşletim sistemlerinin diğer bir görevi de işlemciyi kullanmak için sırada bekleyen proseslere işlemciyi (CPU) dağıtmaktır. Bu görevi üstlenen scheduler (zamanlayıcı), bekleme sırasında bulunan proseslerden hangisinin işlemciyi kullanacağını belirler. Bu sebepten dolayı işletim sistemleri tasarlanırken dikkat edinilmesi gereken en önemli hususlardan birisi zamanlayıcı algoritmasının (CPU scheduling algorithms) verimliliğidir.

Zamanlayıcı algoritmaları preemptive (kesintili) ve nonpreemptive (kesintisiz) olmak üzere 2 farklı gruba ayrılırlar. Bu iki grup arasındaki fark, kesintisiz algoritmalarda işlemci aldığı prosesi tamamlayana kadar başka bir prosese geçmez. Kesintili algoritmalarda ise işlemci aldığı prosesi yarıda bırakıp yeni bir prosesi işleme koyabilir. Bu iki algoritmaya örnek stratejiler aşağıdaki tabloda verilmiştir.

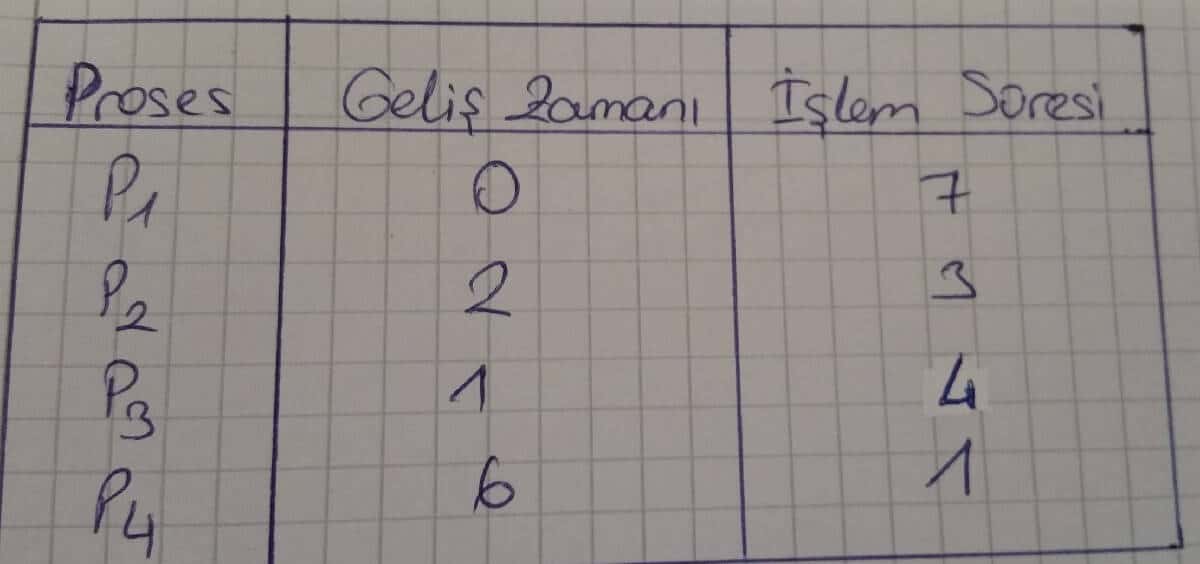

Yukarıdaki resimde 5 ayrı prosesin (P0…P4) bekleme sırasına giriş zamanları ve işlem süreleri verilmiştir.

|

KESİNTİSİZ |

KESİNTİLİ |

|

FIFO |

LIFO-PR |

|

LIFO |

SRPT |

|

SPT |

HRN |

|

ROUNDROBİN |

|

|

EDF |

FIFO:

FIFO (First In First Out) yada diğer bilinen adıyla FCFS (First Come First Served) stratejisinde bekleme sırasına giren prosesler sıranın en başından seçilerek işlemciye aktarılır.

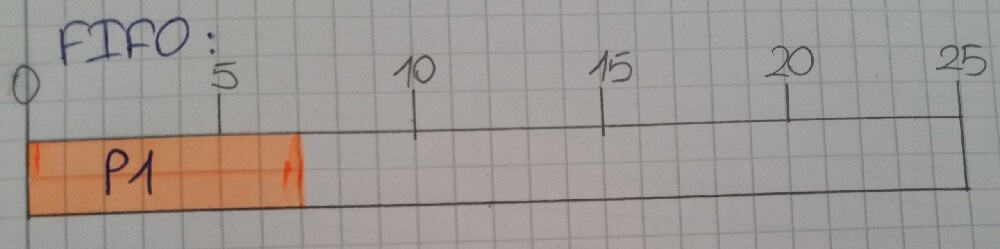

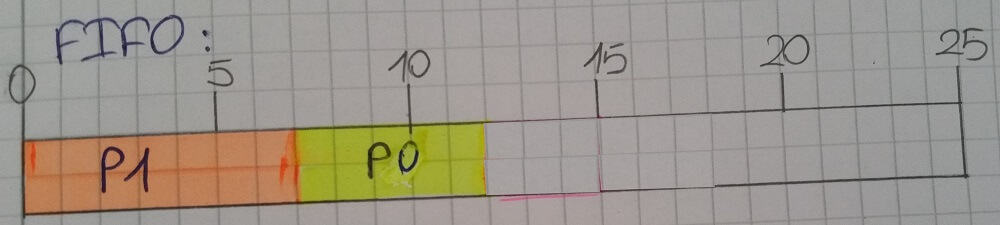

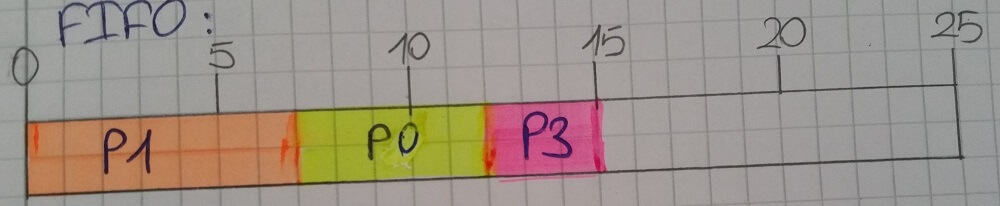

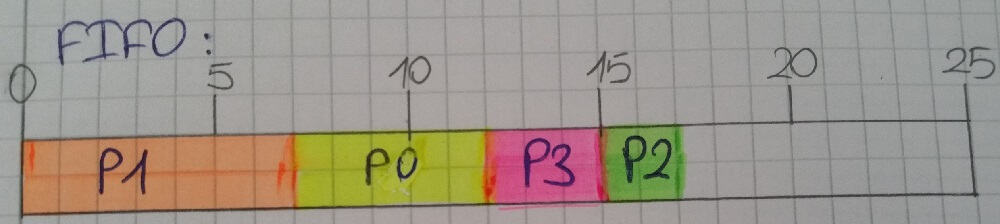

Yukarıdaki proseslerin FIFO stratejisine göre işlemciye eklenmesi:

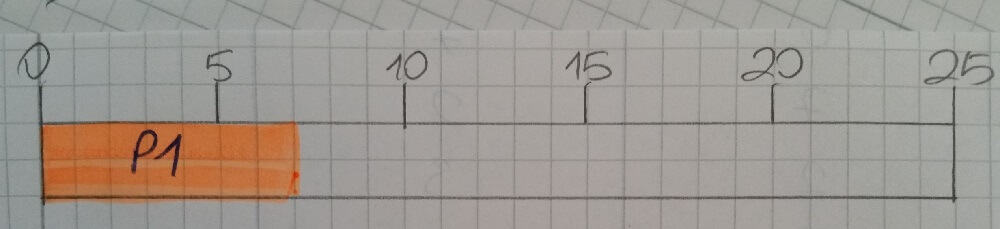

Resimde görüldüğü üzere bekleme sırasına giren ilk proses P1’dir. Bekleme sırasından çıkarılan P1 işlemciye yüklenir ve işlemci 7 birim zaman boyunca P1’i çalıştırır.

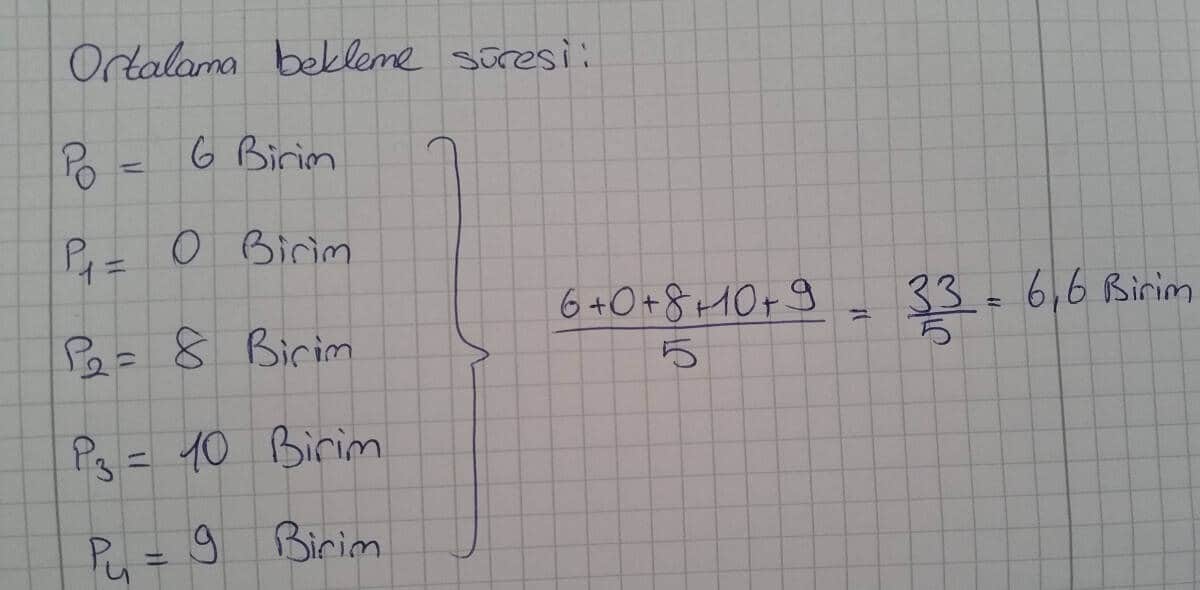

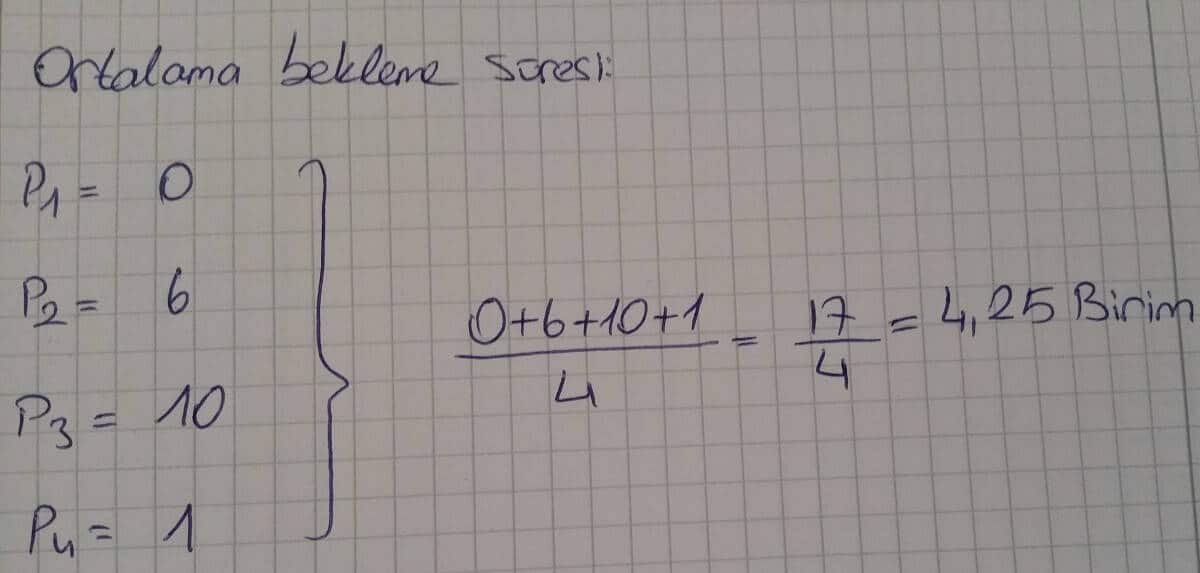

Ortalama bekleme süresi hesaplanırken proseslerin geliş zamanı ve işlemciye alınış zamanları göz önünde bulundurulur.

Bekleme zamanı hesaplama (1 kare = 1 zaman birimi):

0 numaralı prosesin bekleme sırasına giriş yapması gereken zaman proses tablosunda görüldüğü üzere 1. birim zamandır ancak P0’ın işlemciye giriş zamanı 6 birim zaman gecikmiştir. Bu sebepten dolayı P0’ın bekleme süresi 6 birim zaman olarak kaydedilir.

P1’in bekleme sırasına giriş ve işlemciye giriş zamanları aynı olduğu için P1 de herhangi bir gecikme söz konusu olmamıştır. Bu sebepten dolayı gecikme zamanı 0 olur.

Proses 3’ün işlemciye alınma zamanı tabloda 2 olarak verilmiştir ancak oluşan gecikmeden ötürü P3 işlemciye 12. birim zamanda girmiştir. P3′ ün bekleme süresi 12-2 = 10 birimdir.

Bu şekilde işlemciye giren her prosesin bekleme süresi toplanır ve aritmetik ortalamaları alınır:

(6+0+8+10+9) / 5 = 6.6 birim bekleme

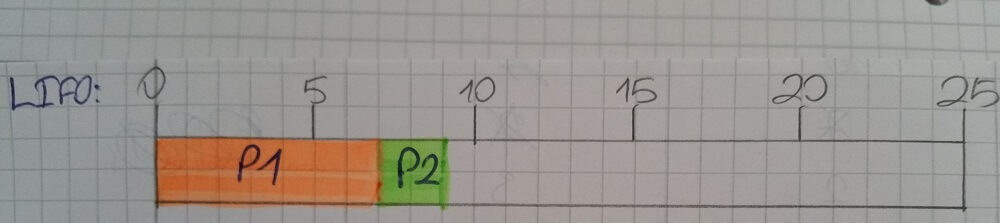

LIFO (Last In First Out) stratejisi FIFO stratejisi ile neredeyse aynı prensipte çalışır. Aradaki tek fark FIFO’da bekleme sırasına giren prosesler, sıranın başından alınırken LIFO’da bekleme sırasının en sonundaki proses işlemciye alınır.

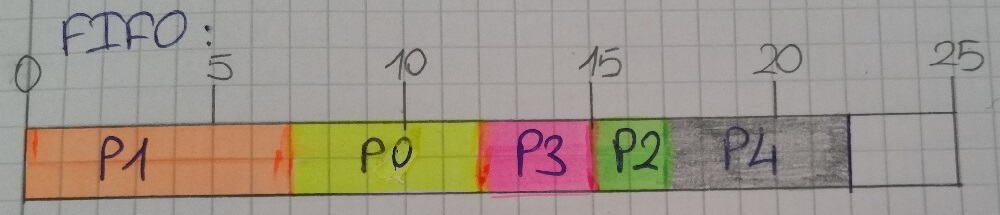

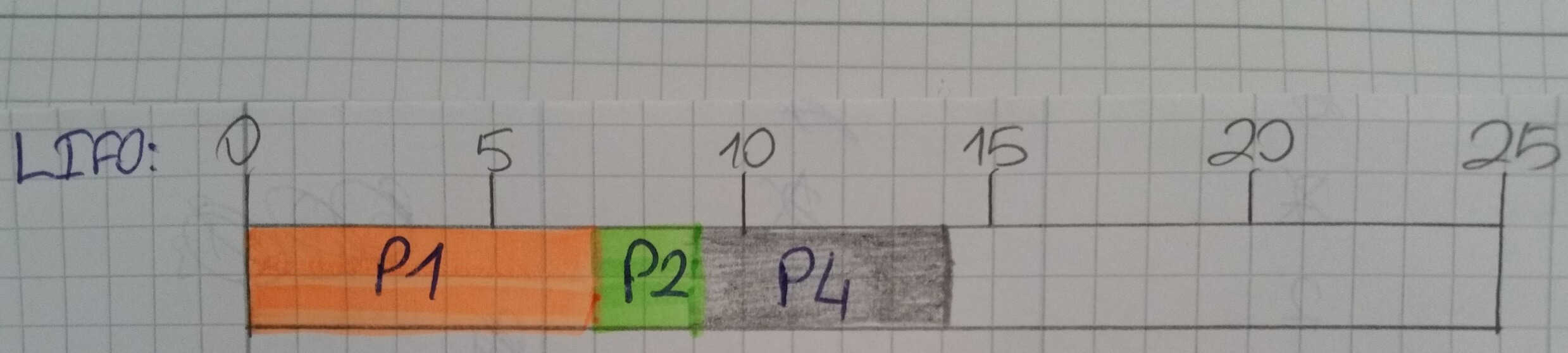

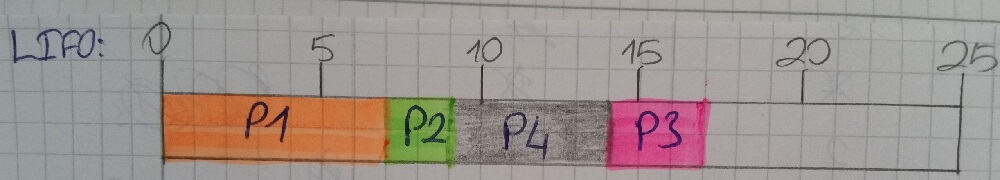

Aynı örnekteki proseslerin LIFO stratejisine göre işlemciye aktarılması:

FIFO stratejisinde olduğu gibi LIFO stratejisi için de bekleme sırasına giren ilk proses P1’dir.

Yeni bekleme sırası = {P0, P3, P4}. P2′ nin ardından işlemciye yeni girecek proses LIFO stratejisinde P4 olur, çünkü P4 bekleme sırasının en sonunda olan prosestir.

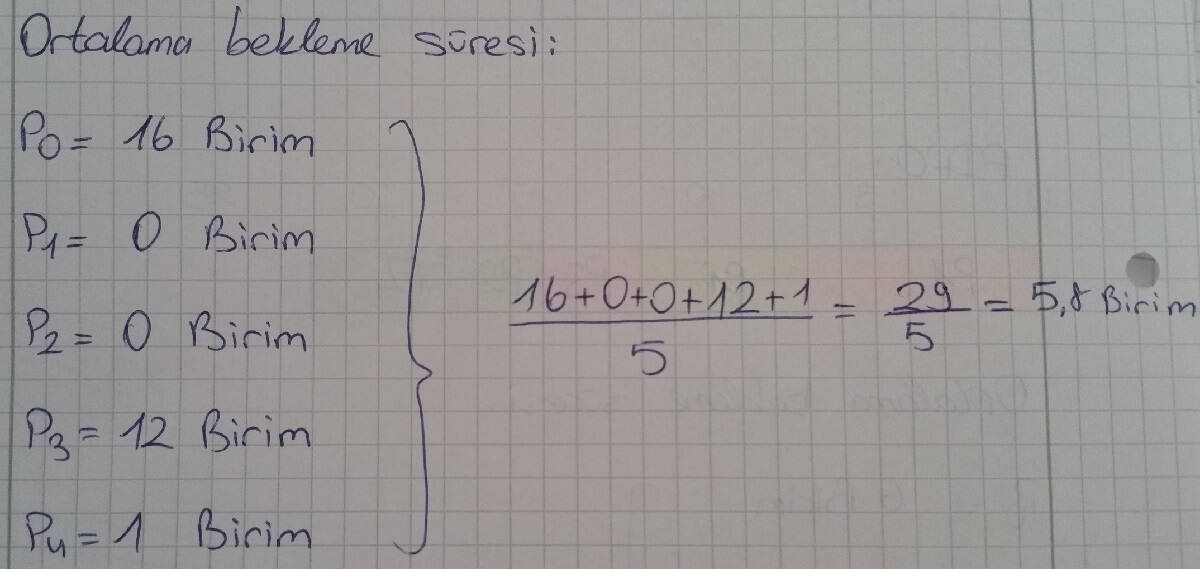

LIFO stratejisinde ortalama bekleme süresi FIFO stratejisinde olduğu gibi hesaplanır.

P0 = İşlemciye 1. birim zamanda girmesi gereken P0 işlemciye 16 birim zaman geç girmiştir.

P1 ve P2 işlemciye giriş zamanları ile bekleme sırasına giriş zamanları aynı olduğu için bu iki prosesin herhangi bir gecikme süresi olmamıştır.

Aynı şekilde P3 ve P4 için bekleme süreleri hesaplanır ve toplam sürenin aritmetik ortalaması alınır.

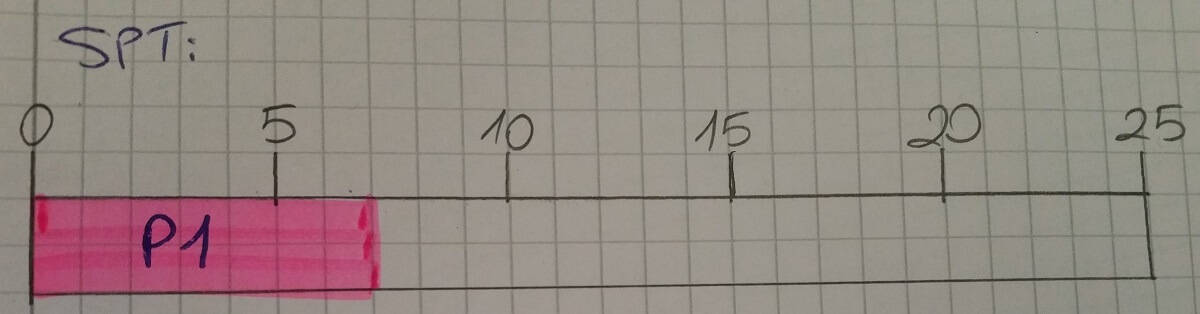

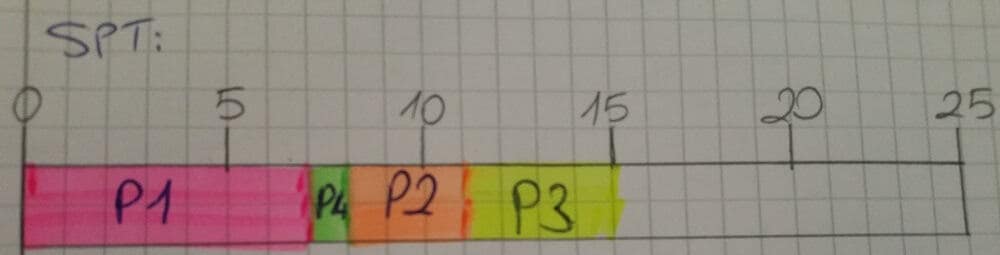

SPT(Shortest Processing Time) stratejisinde, bekleme sırasında bekleyen proseslerin işlem süreleri baz alınarak işlemciye aktarılır. (bu stratejinin oluşturulabilmesi için proseslerin işlem sürelerinin BİLİNMESİ zorunludur.)

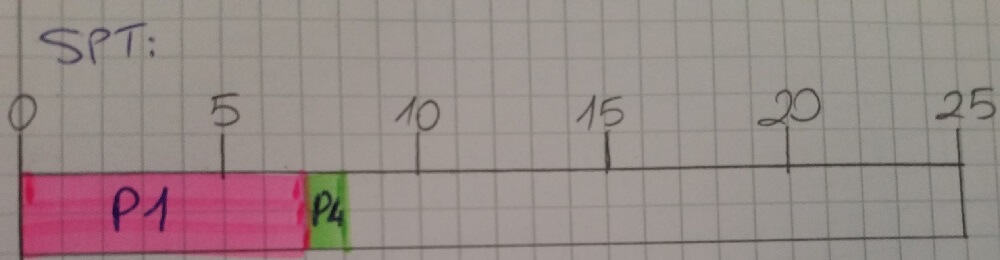

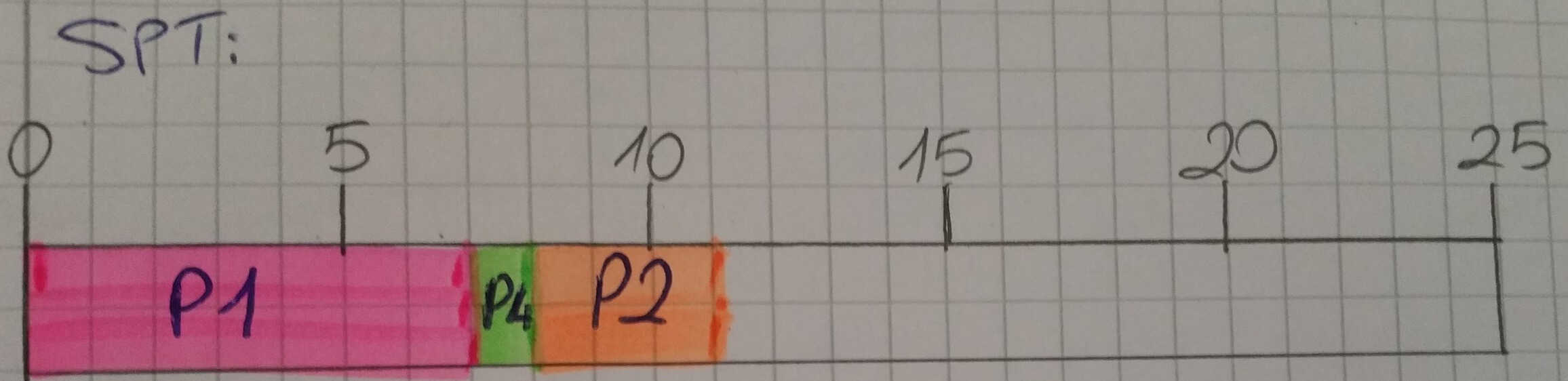

Proseslerin geliş zamanlarına bakıldığında 0. birim zamanda gelen ilk ve tek proesesin P1 olduğu görülür. Bu sebepten dolayı P1 direkt işlemciye aktarılır.

P1 işlemciyi terk ettiği anda işlemciye yüklenecek diğer proses bekleme sırasındaki en düşük işlem süresine sahip olan proses olacaktır. P3, P2 ve P4′ ün işlem süreleri karşılaştırıldığında en düşük işlem süresine sahip olan P4 bekleme sırasından çıkarılıp işlemciye aktarılır.

Diğer stratejilerde olduğu gibi SPT stratejisindede proseslerin toplam bekleme süreleri bulunur ve bu sürenin aritmetik ortalaması alınır.